3o|||sheet is a universal software environment for developing applications for Programmable Logic Controllers (PLCs).

- Hardware Independence

- Integrated Development Environment (IDE)

3o|||sheet is a universal software environment for developing applications for Programmable Logic Controllers (PLCs).

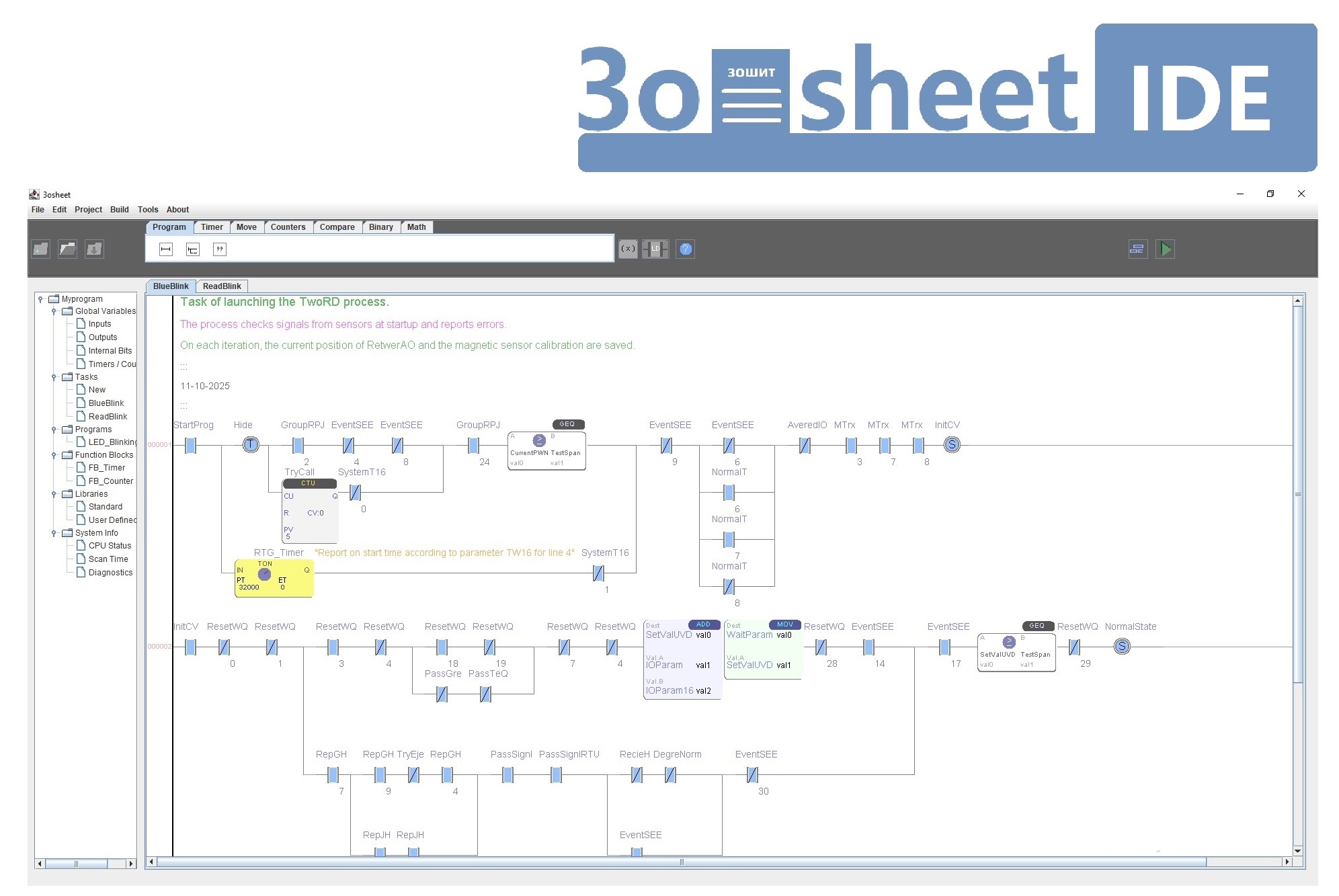

A lightweight, cross-platform IDE built on OpenJDK. Runs on single-board computers with minimal resources.

Supports LD, FBD, and ST languages plus a virtual machine instruction set for advanced logic design.

Offers extensive debugging capabilities: developers can modify code in real-time without physically restarting the PLC.

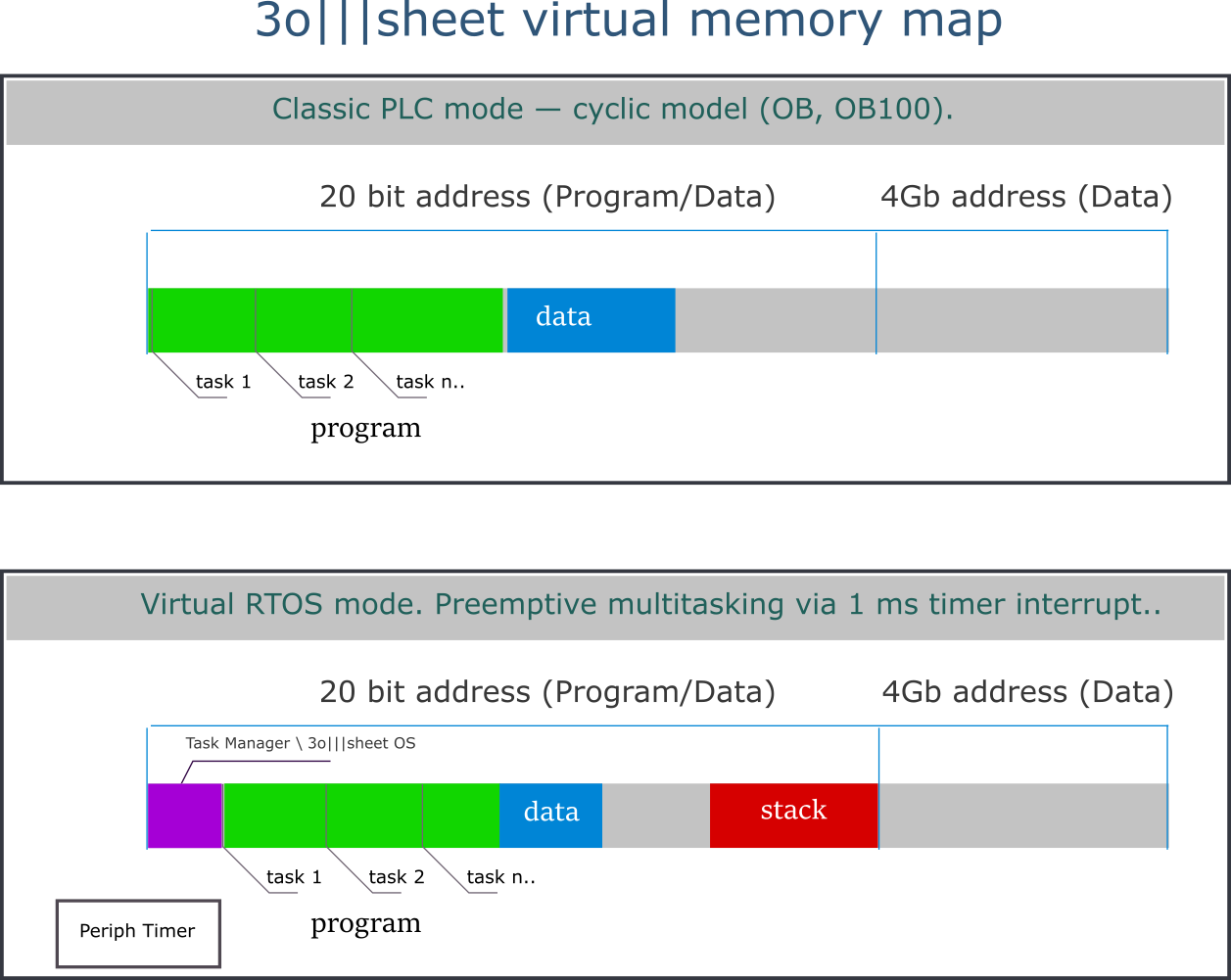

The development environment can create executable programs for the PLC in two modes:

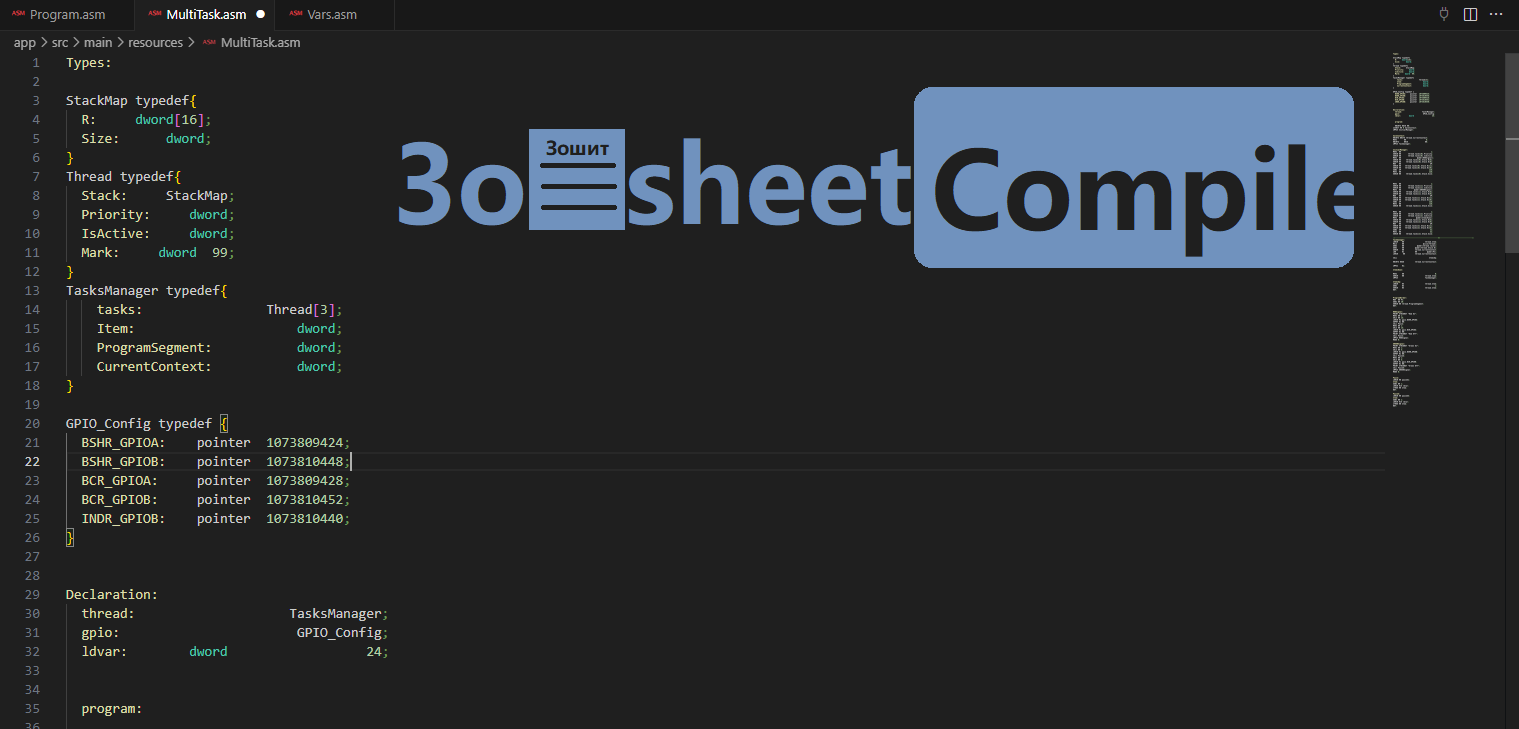

Is a standalone application that compiles text programs written in LD, FBD, ST and .3osheet into executable bytecode for a virtual machine.

The compiler can be integrated into third-party development tools (for example, Visual Studio, etc.).

It includes a complete set of tools for working with complex custom variables, virtual stack, and context management, enabling the development of sophisticated recursive algorithms and multithreaded tasks (coroutines).

Register-based Virtual Machine running safely in a sandbox. Works on devices with only 8 KB RAM and full peripheral access.

Stack and heap dynamically share a contiguous memory area, allowing flexible memory allocation with minimal overhead.

Execute multiple, hardware-isolated runtime environments on a single MCU. Ensures fault containment and enables functional safety.

The platform incorporates a unique divergent architecture designed for maximum reliability and fault tolerance in safety-critical applications. Divergent Multi-Version Execution (DME) is a redundancy-based fault-tolerance architecture that combines address-space decorrelation with per-instruction full-state hashing. Identical instruction bytes are preserved across replicas, while basic blocks are mapped to distinct virtual addresses. After each instruction, replicas compute incremental architectural state hashes and perform synchronous comparison. The approach targets safety-critical embedded systems, particularly 32-bit microcontrollers (e.g., ARM Cortex-M class). DME reduces the probability of undetected replica-local faults by structurally decorrelating control flow without altering program semantics.

Comprehensive fault detection across different execution modes.

| Fault Class | Mode 1 | Mode 2 | Mode 3 |

|---|---|---|---|

| Program flow errors | ✓ YES | ✓ YES | ✓ YES |

| Computation errors | ✗ NO | ✓ YES | ✓ YES |

| Data corruption | ✗ NO | ✗ NO | ✓ YES |

Measured execution times for boolean and Integer and floating-point operations on different microcontrollers and PLCs.

| Device | Boolean Operation | Integer / Floating-Point Operation |

|---|---|---|

| STM32G030 64Mhz (3o|||sheet Runtime) | 2.1 μs | 6.5/24 μs |

| STM32F103 72Mhz (3o|||sheet Runtime) | 1.9 μs | 4.6/4.6 μs |

| STM32F407 168Mhz (3o|||sheet Runtime) | 1.2 μs | 2.8/2.8 μs |

| CH32V203 (144Mhz Mode) (3o|||sheet Runtime) | 0.8 μs | 3.1/18.3 μs |

| CH32V307 144Mhz (3o|||sheet Runtime) | 0.8 μs | 5.5/5.5 μs |

| Rockwell Micro810 | 2.5 μs | 8.6/ - μs |

| Rockwell Compact GuardLogix 5380 1Ghz | ~0.01–0.05 μs | ~0.01–0.08 μs |

| Siemens S7-1200 | ~0.08ns | ~2.3μs/ 4 |